Главная » CADmaster №2(88) 2018 » Электроника и электротехника DDR SDRAM — особенности проектирования и обеспечения целостности сигнала

Сегодня практически невозможно представить современную электронику без модулей памяти. Серверы, компьютеры, смартфоны, игровые консоли, GPS-навигаторы и большинство других устройств спроектированы на основе процессоров и ПЛИС. Такие устройства требуют наличия высокоскоростной памяти с большой пропускной способностью каналов или памяти с двойной частотой передачи данных (DDR). С каждым поколением DDR SDRAM (синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных) появляются новые преимущества, такие как увеличение скорости обмена и емкости, а также снижение энергопотребления.

Основная проблема заключается в том, что использование DDR-памяти при проектировании печатных плат может вызвать ряд сложностей. Проблемы могут возникнуть повсюду — от увеличения стоимости проекта до проблем с целостностью сигналов. В этой статье мы рассмотрим вопросы обеспечения целостности сигналов в устройствах, использующих DDR-память.

Шумы и фазовое дрожание цифрового сигнала данных

Во-первых, нам нужно понять, что происходит на плате при использовании модулей DDR. При приеме/передаче тактового сигнала шины памяти от контроллера к самому чипу могут возникнуть различные помехи, обусловленные собственным джиттером передатчиков и приемников, потерями в линиях передачи, шумами и наводками — всё это вызывает джиттер и порчу формы цифрового интерфейсного сигнала.

В качестве шума можно рассматривать любую нежелательную энергию, добавляемую к идеальному сигналу. Он может быть вызван наводками от соседних линий, плохо спроектированным каналом передачи, несогласованным импедансом и другими факторами, которые приводят к размыванию фронта импульсов. Когда существует шум, он отображается как отклонение от фактического сигнала, если же он отсутствует — фактический сигнал идентичен форме идеального.

Любое отклонение от идеальной формы сигнала влияет на его целостность. Отклонения по времени (джиттер) и отклонения амплитуды/напряжения (шум) также влияют на производительность системы. Если не обеспечить целостность сигналов, то система DDR будет использовать неверную информацию, что значительно увеличит интенсивность битовых ошибок (biterrorrate). В конечном итоге система будет работать некорректно и неэффективно.

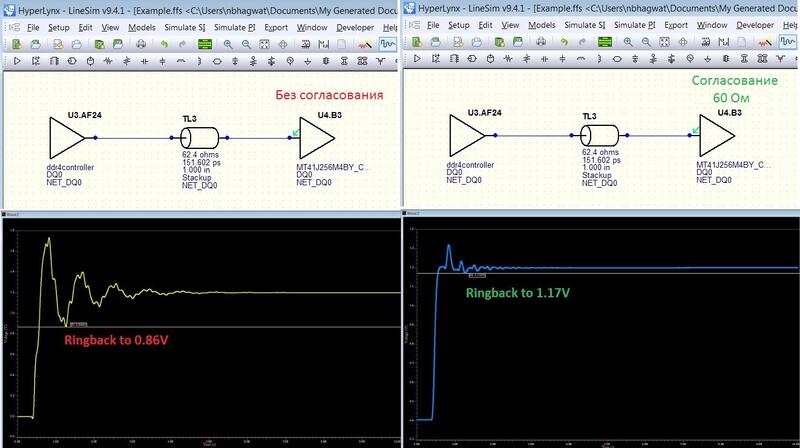

Давайте рассмотрим конкретный пример. Если инженер подключит передатчик к несогласованному приемнику, находящемуся на некотором расстоянии от него, то форма сигнала будет похожа на ту, что представлена на рис. 1а. Здесь отчетливо виден «звон» на уровне 0,86 В и паразитные повышающие выбросы на уровне 1,75 В при 1,2-вольтовом сигнале. Все это может привести к сбою в работе логики DDR4 и, если печатную плату спроектировать с такой топологией, то со стопроцентной вероятностью вы получите ошибки в потоке данных, что в свою очередь может повредить ресиверы.

Теоретически вы можете решить проблемы со «звоном» и выбросами, сократив длину линии передачи, но, к сожалению, это редко работает на практике. Наиболее эффективным способом является согласование приемника/передатчика по импедансу, в результате чего уменьшается уровень шумов и форма сигнала становится значительно лучше (рис. 1б). Сразу возникает вопрос: какой номинал согласования использовать и как его рассчитывать? Ведь даже небольшие изменения номинала могут существенно повлиять на производительность системы. Единственный способ узнать — это симуляция, в частности, с помощью интерактивных помощников настройки согласования, используемых в HyperLynx.

Проблемы тайминга в DDRx

Поскольку параллельные шины, такие как DDR3/4, работающие на гигагерцовых частотах, все чаще и чаще используются при проектировании печатных плат, проблемы целостности сигнала становятся важнее, чем когда-либо.

DDR3 SDRAM, например, существенно отличается в плане скорости работы и показателей частоты от DDR2 — максимальная тактовая частота DDR2 составляет 800 МГц, а максимальная частота DDR3 — 1600 МГц. Благодаря снижению напряжения питания ячеек создателям нового типа ОЗУ удалось снизить ее энергопотребление на целых 15 процентов, что, учитывая впечатляющие показатели DDR2, можно назвать настоящим прорывом. DDR3 использует сетевую «Fly-by»-топологию командной/адресной/управляющей шины с внутримодульным (dynamic On-Die Termination, ODT) согласованием. В то же время DDR3 также создает новые проблемы обеспечения целостности сигнала, в частности, связанные со схемами ODT, более высокими скоростями передачи данных и временными искажениями.

Несмотря на то что имеются контроллеры, которые выполняют автоматическую калибровку чтения/записи, оптимизируя временные интервалы, разработчику все равно необходимо обеспечить правильный тайминг. Временные границы в интерфейсах DDR3 настолько малы, что «правила большого пальца» 1 недостаточно, и необходим подробный анализ дизайна, чтобы гарантировать работу интерфейса на высоких скоростях.

Такие сложные временные соотношения достаточно трудно проанализировать без помощи дополнительных инструментов. Чтобы идентифицировать и устранить возможные проблемы в целом или рассчитать сложные временные соотношения, инженеры должны провести анализ причинно-следственных связей, который является сложной и утомительной задачей.

Подобные проблемы при проектировании часто приводят к задержкам в планировании проектов и, как следствие, значительно увеличивают время выхода готового продукта на рынок. Передовые и мощные инструменты моделирования могут помочь инженерам быстро найти ошибки и исправить их, оптимизировав сигналы до приемлемого уровня BER (Bit Error Rate).

Анализ целостности сигналов DDR SDRAM-систем

Комитет инженерной стандартизации полупроводниковой продукции JEDEC имеет список требований, которые должны соблюдать инженеры, если они хотят разрабатывать качественные продукты. Очень важно, чтобы DDR SDRAM соответствовали этим требованиям для обеспечения правильной работы и предотвращения проблем с целостностью сигнала. Однако провести все необходимые измерения и расчеты — задача не из легких.

Иногда этих расчетов можно вообще избежать, строго следуя инструкциям по компоновке, предоставленным поставщиком контроллера. Но что если такие рекомендации не могут быть выполнены из-за различных ограничений в конкретных проектах? Что делать, если у вас нет времени на то чтобы убедиться, соответствует ли ваш проект всем рекомендованным требованиям? В таких ситуациях вам просто необходимы инструменты для быстрой проверки перед запуском проекта в производство.

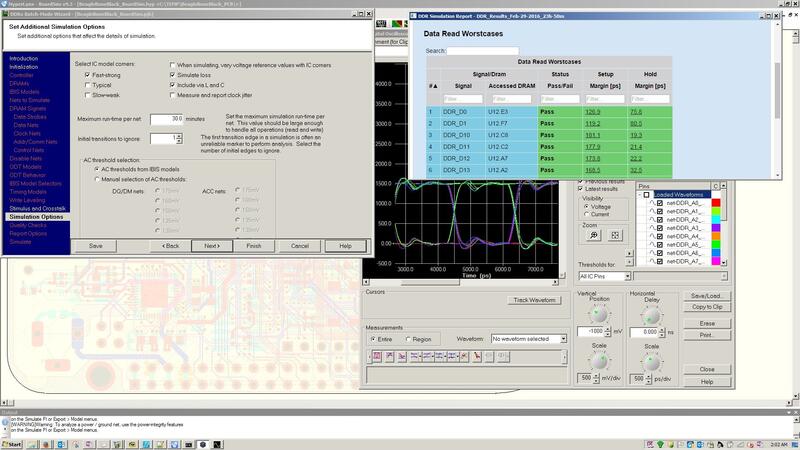

Моделирование — лучшее решение в этих случаях, позволяющее быстро проанализировать ваш проект на наличие проблем целостности сигнала. HyperLynx DDR (рис. 2) позволяет смоделировать весь канал DDR за одну итерацию. Вам нужно только привязать соответствующие модели устройств, которые можно загрузить на сайте поставщиков. После этого время настройки симуляции займет всего десять минут, что позволит в дальнейшем проводить моделирование без задержек.

Процесс настройки интуитивно прост, так как все параметры, необходимые для настройки имитации, запрашиваются помощником в интерактивном режиме. Пользователь просто вводит релевантную информацию, такую как выбор IBIS-моделей для контроллеров и устройств памяти, значения скорости передачи для циклов чтения/записи, ODT и др. Все созданные конфигурации могут быть сохранены для дальнейшего использования, что позволит сократить время настройки в будущих проектах.

Моделирование может выполняться до или после трассировки, помогая вам определять требования к стэкапу печатной платы.

Анализ результатов моделирования

Моделирование включает в себя анализ целостности сигналов и синхронизацию всей шины DDR. По завершении процесса симуляции создается отчет, который включает в себя данные о прохождении/непрохождении проверок в соответствии с информацией о вашей конфигурации, на основе данных, которые вы ввели в интерактивный помощник. Результаты могут быть отфильтрованы, позволяя вам внимательно изучить тайминги и проблемы SI (Signal Integrity) в циклах чтения/записи данных, в адресной и командной шинах или дифференциальных цепях. Все результаты отчета привязаны к соответствующим данным моделирования — для быстрого доступа к средству просмотра графических осциллограмм соответствующих сигналов.

Данные моделирования в пакетном режиме, созданные мастером DDRx, могут быть сохранены на диск, поэтому вы можете использовать осциллограф HyperLynx для одновременной симуляции нескольких цепей и подробного изучения проблем целостности сигналов в автономном режиме.

Заключение

DDR SDRAMs привнесли новые и мощные возможности разработки электронных устройств. Как и в случае с другими высокоскоростными интерфейсами, память DDR имеет ряд нюансов. Целостность сигнала — это важный аспект, который необходимо тщательно изучать, чтобы избежать лишних и дорогостоящих итераций при производстве изделий. Моделирование — отличный способ обеспечить целостность сигнала, позволяющий вам учитывать эффекты на уровне платы, такие как изменения импеданса и задержки по времени, обеспечивающий всесторонний контроль над интерфейсом памяти. Мощные инструменты анализа помогут добиться соответствия ваших проектов рекомендациям JEDEC и быть уверенными в том, что ваш конечный продукт будет работать с высокой производительностью и скоростью.

HyperLynx DDR доступен для использования с несколькими САПР проектирования печатных плат, включая PADS и Xpedition.

- «Правило большого пальца» (англ. rule of thumb) — практический способ, метод, эмпирическое правило. ↑

Скачать статью в формате PDF — 1.06 Мбайт |