# ПОЛЕЗНЫЕ СОВЕТЫ ПО ИСПОЛЬЗОВАНИЮ HyperLynx DDR Wizard ДЛЯ АНАЛИЗА QDR-IV

# Введение

Quad Data Rate (QDR-IV) является стандартом высокопроизводительной памяти для сетевых применений и идеально подходит для нового поколения сетевых устройств, коммуникационного оборудования и вычислительных систем.

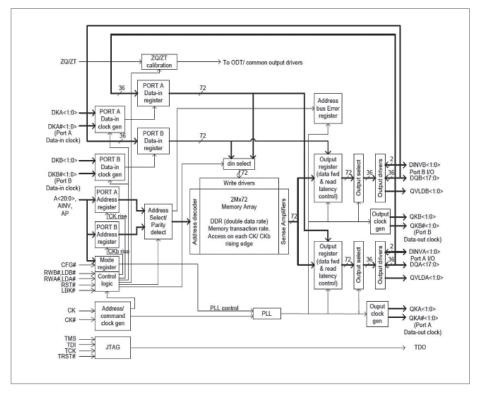

QDR-IV SRAM-память имеет встроенный блок обнаружения и коррекции ошибок (ЕСС), обеспечивающий целостность данных. Этот блок способен обработать все одноразрядные ошибки памяти, в том числе вызванные космическими лучами и альфа-частицами. В результате модули памяти будут иметь коэффициент ошибок программ (SER) не более 0,01 сбоев/МБ. QDR-IV снабжена функцией программируемой чётности адреса, которая обеспечивает целостность данных на адресной шине (рис. 1). Отличительные особенности ODR SRAM-памяти:

- встроенный модуль коррекции ошибок, обеспечивающий целостность данных и исключающий программные ошибки;

- модули доступны в двух версиях:

QDR-IV HP (скорость передачи данных 1334 Мтранз/с) и QDR-IV XP (скорость передачи данных 2132 Мтранз/с);

- два независимых двунаправленных порта данных памяти DDR1;

- функция инверсии шины для снижения шумов при одновременном подключении линий ввода и вывода;

- встроенная схема согласования (ODT), уменьшающая сложность

- тренинг на перекос для улучшения временных характеристик захвата сигнала;

- уровень сигналов ввода-вывода: от 1,2 В до 1,25 В (высокоскоростная

- приемопередающая логика (HSTL)/ терминированная логика (SSTL)), от 1,1 В до 1,2 В (POD2);

- 61-выводной корпус FCBGA3;

- разрядность шины: x18, x36 бит.

DDRx Wizard является простым в использовании инструментом HyperLynx, который позволяет в пакетном режиме

Рис. 1. Внутренняя архитектура QDR на примере модуля CY7C4142KV13

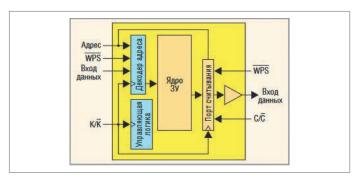

Рис. 2. Наличие раздельных портов считывания и записи в архитектуре QDR SRAM

ключен.

(рис. 3а и 3б).

три сценария тестов.

гой для записи), которые поддерживают независимую друг от друга работу и одновременные операции считывания и записи, причем порты могут работать на разных частотах (рис. 2). Таким образом, риск сбоя работы полностью ис-

Для этого протокола DDRx Wizard будет использовать отдельные стробы для операций чтения и записи данных. QDR-IV обычно реализуется с помо-

щью х36- или х18-разрядной шины

DDRx Wizard позволяет проводить моде-

проверка шины адреса/управления. Проверку шины адреса/управления можно проводить независимо от проверок чтения/записи данных, это может сэкономить вам время за счет совмеще-

ния этого этапа с любым из этапов те-

стирования данных. Далее описаны все

лирование QDR-IV в три этапа: проверка чтения данных; проверка записи данных;

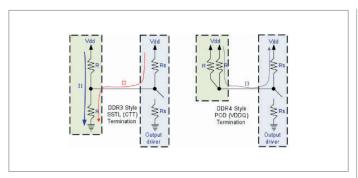

Рис. 4. Различия POD и SSTL

Рис. 3a. QDR-IV, x36-бит

RANIES DENNIS PARTES DEVENTE

Рис. 36. QDR-IV, x18-бит

контролировать временные осциллограммы и проводить анализ целостности сигнала стандартных протоколов DDR JEDEC. DDRx Wizard может быть запущен как на этапе предтопологического анализа по сценарию "что, если", так и на полностью оттрассированной плате. Кроме того, инструмент поддерживает импорт большинства форматов моделей, созданных крупными поставщиками микросхем.

DDRx Wizard позволяет проверить все биты шины памяти на соответствие целостности сигнала, а также на соответствие требованиям синхронизации между сигналами. В этой статье будет подробно представлено использование интерактивного помощника для анализа проектов, реализующих протокол QDR-IV.

# Первый взгляд на QDR-IV в HyperLynx DDRx Wizard

Протокол ODR-IV определяет две однонаправленных пары сигнала строба данных (один для считывания данных, дру-

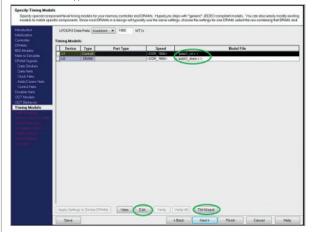

Технологические особенности QDR-IV поддерживает технологию "псевдооткрытый сток" (POD) и терминирующую логику Stub Series Terminated Logic (SSTL) (рис. 4). Независимо от используемого стандар-

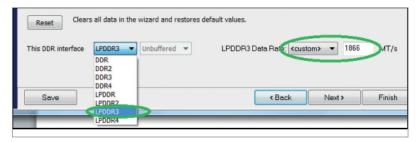

та логики выберите LPDDR3 в качестве технологии (рис. 5), так как здесь нет поддержки Vreftraining, как в случае с модулем DDR4's POD. Вместо этого используются фиксированные значения Vref и Vinh/Vinl, аналогичные DDR3 и LPDDR3. Поскольку QDR-IV использует двойную скорость передачи данных для адресных сигналов, подобных LPDDR3, рекомендуется выбрать эту опцию. Далее введите скорость передачи пользовательских данных - например, 1866 MT/s или 2133 MT/s, где MT/s – число мегатранзакций в секунду (megatransfers per second).

Рис. 5. Выбор стандарта логики

Рис. 6. Чтение данных

Рис. 8. Настройка значения тайминга

Рис. 7. Чтение строба данных

Рис. 7а. Группа сигналов для 36-разрядной шины

Рис. 76. Группа сигналов для 18-разрядной шины

# Сигнал данных: операция чтения

Для операций чтения сигнала данных DRAM будет управлять сигналами DQ совместно с дифференциальными стробами сигналами QK. Таким образом, настройка фокусируется на операции чтения данных и назначает нужные цепи (сигналы) к соответствующему QK стробу.

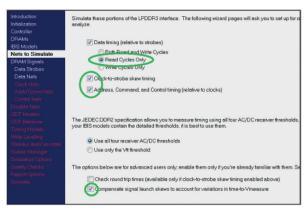

В разделе Nets to Simulate (рис. 6) установите чекбокс "Только циклы чтения" (Read Cycles Only). Чекбоксы Clock-to-strobe и Address checks не являются обязательными.

Также проверьте установку чекбокса Compensate signal launch skews to account for variations in time-to-Vmeasure.

Убедитесь, что выбраны все необходимые стробы данных (рис. 7).

В разделе **Data Nets** проверьте правильность соответствия сигналов каждому стробу. Обратите внимание, что для х18-и х36-разрядных шин сигналы отличаются, поэтому убедитесь в правильности распиновки конкретно под ваш случай (рис. 7а и 76).

Проверка параллельных шин обычно выполняется установкой/выдержкой времени между стробом и сигналом. Все эти требования, в дополнение к другим

временным значениям, необходимы мастеру DDRx Wizard для проверки результатов. Эти значения могут отличаться от микросхемы к микросхеме, поэтому рекомендуется вводить значения, применимые к конкретному устройству памяти. Кроме того, информация о тайминге по умолчанию для LPDDR3 несовместима с QDR-IV. Итак, вся информация по таймингам для QDR-IV должна быть введена и соответствовать документации на вашу микросхему.

Это можно сделать с помощью мастера синхронизации (Timing Wizard) (рис. 8), который предлагает пользователю заполнить несколько форм для последующей генерации временных значений. Также вы можете отредактировать .V-файлы синхронизации, соответствующие вашему контроллеру и DRAM.

Для лучшего понимания обратитесь к веб-сайту Mentor Graphics SupportNet, где размещена информация о создании моделей синхронизации:

- создание и поиск DDRх-моделей синхронизации контроллера памяти (Creating and Finding DDRх Memory Controller Timing Models);

- определение допустимых отклонений в таблице модели контроллера

- DDRx (Defining a Derating Table in DDRx Controller Timing Models);

- таблица отклонений для моделирования DDR3 с помощью пакетного мастера DDRx Batch Wizard без заранее определенной таблицы отклонений (Derating Table of DDR3 Simulation Using the DDRx Batch Wizard without a Pre-Defined Derating Table).

Поскольку моделирование выполняется в режиме LPDDR3, то и результаты должны быть интерпретированы соответствующим образом.

## Сигнал данных: операция записи

Операция записи данных и ее анализ подобны анализу для операции чтения, но есть два ключевых отличия, которые мы рассмотрим ниже. За исключением этих двух нюансов, шаги, выполняемые для операции чтения данных, можно повторить для симуляции записи данных.

В разделе Nets to Simulate (рис. 9) убедитесь, что выбран параметр Write Cycles Only.

Также существует возможность имитировать операции записи адресного сигнала (Address Signal write Operations). И не забудьте убедиться, что установлен фла-

Рис. 9. Запись данных

Рис. 10. Стробы данных записи

Рис. 11. Группы сигналов строба записи (36-разрядной шины)

Lot for data areh afrone kinsy you want'u messure. You can include a fire simulation any or all of the biboring one, data bits COQ data masks (EM), and deach bits COQ collection and control of the biboring one, data bits COQ data masks (EM), and deach bits COQ collection and control of the biboring one, data bits COQ data masks (EM), and deach bits COQ collection and control of the biboring one, data bits COQ data mask rath must be separately destricted from precision of the biboring one, data bits COQ data masks (EM), and destruction a

Рис. 12. Группы сигналов строба записи (18-разрядной шины)

Рис. 13. Установите флажок Address, Command, and Control timing

Рис. 14. Выбор дифференциального синхросигнала

жок Compensate signal launch skews to account for variations in time-to-Vmeasure. Убедитесь, что в разделе Data Strobe выбраны правильные стробы (рис. 10). Ключевое различие между транзакцией чтения и транзакцией записи — это строб, используемый для синхронизации данных; этот строб отличается от строба, используемого для операции чтения данных (рис. 11 и 12).

### Шина адреса, команд и управления

QDR-IV использует дифференциальные клоки СК/СК# для выбора сигналов управления, адреса и командных сигналов. Передний фронт сигнала СК используется для ввода информации о порте A, а задний — для отбора информации о порте B.

Принимая во внимание обеспечение целостности сигнала, осциллограммы для адресных линий должны соответствовать требованиям к установке и задержкам как переднего, так и заднего фронта тактового сигнала. Это очень похоже на поведение LPDDR3.

Сигналы LDA#, LDB#, RWA# и RWB# синхронизируются с одной скоростью передачи данных (single-data-rate). Значит, эти сигналы синхронизируются только на одном из двух фронтов тактовых импульсов. Сигналы LDA# и RWA# синхронизируются по нарастающему фронту синхроимпульса, а сигналы LDB# и RWB# – по спадающему фронту. Клоки в значительной степени симметричны – передний дифференциальный фронт не сильно отличается от заднего. Это означает, что для обеспечения целостности сигналов значения тайминга для LDB# и RWB# должны быть почти одинаковыми (если не идентичными) при выборке на переднем или заднем фронте синхросигнала. Сигналы управления LPDDR3 синхронизируются также только по переднему фронту.

Следующие шаги специфичны для моделирования шин адреса, команд и управления при использовании QDR-IV.

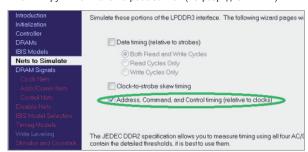

Убедитесь, что в разделе Nets to Simulate установлен флажок Address, Command, and Control timing (relative to clocks) (рис. 13).

В разделе **Clock Nets** удостоверьтесь, что выбрана дифференциальная пара тактовых сигналов СК/СК# (рис 14).

В разделе Addr/Comm Nets убедитесь, что биты A [20:0] выбраны для устройств с разрядностью х36, а биты A [19:0] — для устройств с разрядностью х18. Кроме того, задайте сигналы AP и AINV (рис. 15 и 16). В разделе Control Nets выберите сигналы LDA#, LDB#, RWA# и RWB# (рис. 17).

Как и в случае моделирования сигнала данных, убедитесь, что вы используете правильные файлы с параметрами тайминга. Остальная часть моделирования и оценки результатов аналогична LPDDR3.

### Заключение

Следуя несложным инструкциям, приведенным в этой статье, можно получить большую пользу и эффективно использовать пакет помощника DDRx Wizard при моделировании и проверке шин QDR-IV.

Богдан Филипов AO "Нанософт" Тел.: (495) 645-8626 E-mail: filipov@nanocad.ru

Рис. 15. Настройки для х36-битных шин

Рис. 16. Настройки для х18-битных шин

Рис. 17. Сигналы управления